FlexyICE: Difference between revisions

m (moved Artecgroup programmable LPC dongle to FlexyICE: the official product name is now FlexyICE, so let's call the page like that, too. Old name will be forwarded to the new one.) |

No edit summary |

||

| Line 1: | Line 1: | ||

[[Image:artec_dongle.jpg|thumb|right| | [[Image:artec_dongle.jpg|thumb|right|Artec Group FlexyICE (version 1).]] | ||

== About the | == About the FlexyICE == | ||

The dongle is | The FlexyICE (formerly known as LPC dongle) is made by [http://www.artecgroup.com/products/hardware-products/programmable-lpc-dongle.html Artec Group], based in Estonia. It costs about EUR 160 (2009-11). | ||

The | The FlexyICE connects to a computer via USB. It connects to the target via an LPC header. | ||

The | The FlexyICE comes with [http://opencores.org/projects.cgi/web/usb_dongle_fpga/overview free software and full schematics] (scroll all the way to the bottom for download links, or click on the CVS: browse link near the top). The host-based software is written in Python, and works just fine under GNU/Linux. | ||

The | The FlexyICE has 16 MByte of onboard memory, divided in 4 banks of 4 Mbyte each. The 'mode-selection' jumpers allow selection of each bank: 00, 01, 10, 11. | ||

The dongle also has two 16-segment LED displays that can show POST codes. | The dongle also has two 16-segment LED displays that can show POST codes. | ||

| Line 15: | Line 15: | ||

If you hold the reset button on the dongle, the second LED will show the version of the VHDL you have - currently 03, 04 or 05. | If you hold the reset button on the dongle, the second LED will show the version of the VHDL you have - currently 03, 04 or 05. | ||

Artec Group provides [http://opencores.org/cvsweb.shtml/usb_dongle_fpga/release/EPCS_update_tool.zip a tool] to upgrade the VHDL on the dongle that can be run under GNU/Linux (it's a python program). They also provide the binary image for the v5 of the VHDL. Of course all sources are available to build that binary image, but currently proprietary software on Windows is needed to do so. You will need a byteblaster-II cable (which can be purchased at http://www.customcircuitsolutions.com/cable.html or http://fpgaguy.110mb.com/, for instance). This tool has only received limited testing, so please be careful and report any problems to the author. | |||

== Using the dongle == | == Using the dongle == | ||

| Line 68: | Line 68: | ||

</pre> | </pre> | ||

The | The Artec Group LPC dongle has a 10-pin LPC dongle that is described [http://www.artecgroup.com/downloads/task,doc_download/gid,5/Itemid,33/ in the schematics]. This is the pin layout: | ||

<pre> | <pre> | ||

| Line 111: | Line 111: | ||

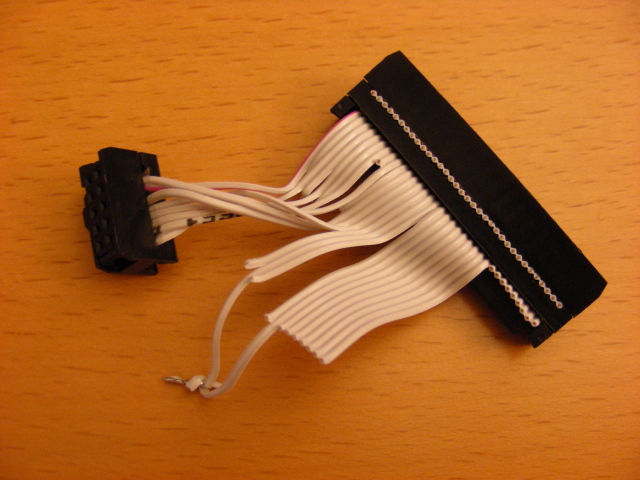

This is what a finished cable looks like: | This is what a finished cable looks like: | ||

[[Image:Dscn3151_640_480.jpg||Custom ALIX.1C to | [[Image:Dscn3151_640_480.jpg||Custom ALIX.1C to Artec Group LPC dongle cable]] | ||

You can test your cable by booting the ALIX.1C, and then hooking it up to the dongle (using J16 on the ALIX.1C, of course). Now reboot the ALIX.1C board; the LEDs on the dongle should show post codes as the ALIX.1C shuts down and tries to boot. Unless you've prepared the dongle and stored an image into it, the ALIX.1C will not boot. But if you see POST codes on the LEDs, your cable is likely to be good. If not, use a multimeter and make sure it matches the layout above. Also make sure that it is not too long. | You can test your cable by booting the ALIX.1C, and then hooking it up to the dongle (using J16 on the ALIX.1C, of course). Now reboot the ALIX.1C board; the LEDs on the dongle should show post codes as the ALIX.1C shuts down and tries to boot. Unless you've prepared the dongle and stored an image into it, the ALIX.1C will not boot. But if you see POST codes on the LEDs, your cable is likely to be good. If not, use a multimeter and make sure it matches the layout above. Also make sure that it is not too long. | ||

Revision as of 17:21, 3 November 2009

About the FlexyICE

The FlexyICE (formerly known as LPC dongle) is made by Artec Group, based in Estonia. It costs about EUR 160 (2009-11).

The FlexyICE connects to a computer via USB. It connects to the target via an LPC header.

The FlexyICE comes with free software and full schematics (scroll all the way to the bottom for download links, or click on the CVS: browse link near the top). The host-based software is written in Python, and works just fine under GNU/Linux.

The FlexyICE has 16 MByte of onboard memory, divided in 4 banks of 4 Mbyte each. The 'mode-selection' jumpers allow selection of each bank: 00, 01, 10, 11.

The dongle also has two 16-segment LED displays that can show POST codes.

If you hold the reset button on the dongle, the second LED will show the version of the VHDL you have - currently 03, 04 or 05.

Artec Group provides a tool to upgrade the VHDL on the dongle that can be run under GNU/Linux (it's a python program). They also provide the binary image for the v5 of the VHDL. Of course all sources are available to build that binary image, but currently proprietary software on Windows is needed to do so. You will need a byteblaster-II cable (which can be purchased at http://www.customcircuitsolutions.com/cable.html or http://fpgaguy.110mb.com/, for instance). This tool has only received limited testing, so please be careful and report any problems to the author.

Using the dongle

Drivers for Windows and Mac OS

The dongle can be accessed using its usb-to-serial chip (FT245B(M)). For Windows and Mac OS, you need a driver for the chip, which can be found at the chip vendor's website.

Reading from and writing to the dongle

If you use Ubuntu, make sure to uninstall brltty (apt-get remove brltty --purge) before you hook up the dongle; otherwise it will hijack the dongle and you won't be able to talk to it. Brltty is a software braille terminal.

Images are downloaded via USB. With the latest version of the VHDL (v5), it should take about 8 seconds to write a 512KByte image to the dongle.

Here's a command that writes a 512KByte image to the dongle

./dongle.py -v -c /dev/ttyUSB0 alix0-1.bin 3584K

The -v parameter makes the command verbose. -c /dev/ttyUSB0 means 'use device /dev/ttyS0'. Alix0-1.bin is the image that is to be written to the dongle (it's a 512KByte file), and 3584K is the offset at which it should be written. Always calculate that number as 4Mbyte - size of your image.

And here's how you can read the image back:

./dongle.py -c /dev/ttyUSB0 -r 3670016 512K test2.rom

The -r parameter indicates 'read', and 3670016 is the offset at which the program should start reading (this is 3584K), for 512K bytes. You can express the offset in decimal (like in this example, in hex with a leading 0x, or in abbreviated decimal - for instance 3584K). Test2.rom is the file the image will be stored in on your computer.

If you actually wrote and read an image, you should now md5sum both files to make sure they are identical.

Booting an ALIX.1C

First of all, you'll need to make a custom cable. The ALIX.1C has a 20-pin header (J16) that can be used to hook up the dongle. The pin layout is documented on page 13 and 14 in the ALIX.1C manual:

1 LCLK0 LPC clock (33 MHz) 2 GND ground 3 LAD0 LPC data 0 4 GND ground 5 LAD1 LPC data 1 6 GND ground 7 LAD2 LPC data 2 8 GND ground 9 LAD3 LPC data 3 10 GND ground 11 LFRAME# LPC frame 12 GND ground 13 PCIRST# reset (active low) 14 NC reserved 15 ISP high to use LPC flash, low to use on-board flash, pulled low by resistor 16 VCC +5V supply 17 GND ground 18 V3 +3.3V supply 19 SERIRQ serial interrupt 20 LDRQ# LPC DMA request

The Artec Group LPC dongle has a 10-pin LPC dongle that is described in the schematics. This is the pin layout:

1 RESETX 2 LAD0 3 LAD1 4 LAD2 5 LAD3 6 LFRAME# 7 R33 GND 8 PCICLK1 9 GND 10 VCC 3V in

Peter Stuge figured out the correct wiring here and here. This is the wiring diagram:

Dongle - ALIX.1C

1 - 13

2 - 3

3 - 5

4 - 7

5 - 9

6 - 11

7 - NC

8 - 1

9 - 2/4/6/8/10/12/17 (just pick one)

10 - NC

- 15 connected to 18

In the above, pin 7 on the dongle should not be connected to anything on the ALIX.1C. Pin 9 on the dongle should be connected to one of 2/4/6/8/10/12/17 on the ALIX.1C, not all of those pins. Pin 15 and 18 on the ALIX.1C side need to be shorted, but not connected to anything on the dongle side.

Cable length is important - your cable should not be more than a few centimeter long.

The easiest way to make such a cable is to take an old floppy or IDE-40 flat ribbon cable (don't use IDE-80, its wires are much thinner which makes things harder), cut it, and put a 10-pin header on the dongle side.

If you are in the US, you can buy 10-pin headers here (Jameco part number 32492). You might also want to get a crimping tool (Jameco part number 73252).

This is what a finished cable looks like:

You can test your cable by booting the ALIX.1C, and then hooking it up to the dongle (using J16 on the ALIX.1C, of course). Now reboot the ALIX.1C board; the LEDs on the dongle should show post codes as the ALIX.1C shuts down and tries to boot. Unless you've prepared the dongle and stored an image into it, the ALIX.1C will not boot. But if you see POST codes on the LEDs, your cable is likely to be good. If not, use a multimeter and make sure it matches the layout above. Also make sure that it is not too long.

Now make sure the dongle is correctly configured:

Jump pin 1/2 on J1. Make sure JMP4 is set to position 1/2 (i.e. NOT to the pins marked as LPC). Make sure that you leave the mode select jumpers in the same position between the writing of the image into the dongle and trying to boot off it.

Now write your image to the top of the memory bank you want to use (see higher). Then disconnect the dongle from your computer, reconnect it, make sure that you have your cable connected to the LPC port on the dongle and J16 on the ALIX.1C, and plug in power to the ALIX.1C. Also hook up a serial port to the ALIX.1C so that you see what happens during boot. If all goes well, you will see post codes on the dongle LEDs as the ALIX.1C boots.

Booting FWH PLCC boards

It is also possible to boot FWH PLCC boards, if you make a special cable. For an example of such a cable, see some photos here: http://www.artecdesign.ee/~martr/dongle-fwh-plcc-cable/. TODO: we need to find a place to buy such a connector, and we need to document the pinout of the cable.

Booting SPI boards

With a VHDL change and the proper cable, it should be possible to use the dongle to boot SPI-based boards. Artec is considering this as a planned feature for Artec Dongle II VHDL - when that is done, interested parties can try to backport the relevant open source VHDL parts.

|

This work is free software; you can redistribute it and/or modify it under the terms of the GNU General Public License as published by the Free Software Foundation; either version 2 of the License, or any later version. This work is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU General Public License for more details. |