Board:lenovo/t530: Difference between revisions

Eocallaghan (talk | contribs) mNo edit summary |

MartinRoth (talk | contribs) |

||

| Line 70: | Line 70: | ||

== Flashing == | == Flashing == | ||

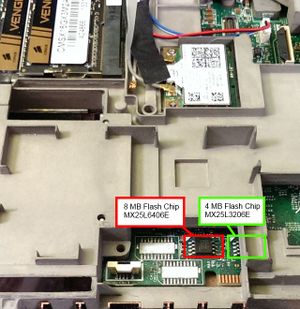

[[File:T530_SPI_chips.jpg|thumb|Location of the SPI chips]] | |||

T530 has 2 flash chips of 8M and 4M. They're concatenated to one virtual flash chip of 12M which is itself subdivided in roughly in 4 parts: | T530 has 2 flash chips of 8M and 4M. They're concatenated to one virtual flash chip of 12M which is itself subdivided in roughly in 4 parts: | ||

| Line 78: | Line 81: | ||

ME firmware is not readable. | ME firmware is not readable. | ||

Vendor firmware locks the flash and so you need to flash externally (unless until someone figures out a way around it). | Vendor firmware locks the flash and so you need to flash externally (unless until someone figures out a way around it). | ||

Proceeds as follows: | Proceeds as follows: | ||

* Turn off your laptop, remove battery and AC adapter. | * Turn off your laptop, remove battery and AC adapter. | ||

* Remove the keyboard. | * Remove the keyboard. | ||

* Connect your external SPI flasher to the top SPI chip which is under palm resting space, on left side of the board. It's a 4M chip. IF you've chosen CBFS_SIZE 4M or smaller that' the only chip you need to reflash. | * Connect your external SPI flasher to the top SPI chip which is under palm resting space, on left side of the board. It's a 4M chip. IF you've chosen CBFS_SIZE 4M or smaller that's the only chip you need to reflash. | ||

I recommend using SOIC clip. Depending on the flasher you use, you may have to use separate | I recommend using SOIC clip. Depending on the flasher you use, you may have to use separate | ||

| Line 95: | Line 97: | ||

diff flash.bin flash2.bin | diff flash.bin flash2.bin | ||

If they don't match, do not proceed. If the file is 8M, you're flashing wrong chip, | If they don't match, do not proceed. If the file is 8M, you're flashing wrong chip, connect to the right one. | ||

* Write the flash. Since you have to write only top 4M, first split out those 4M: | * Write the flash. Since you have to write only top 4M, first split out those 4M: | ||

Revision as of 19:01, 19 June 2014

Specification

The machine has:

- Chipset: Intel QM77

- GPU's: Intel Integrated HD Graphics

: Discrete NVIDIA NVS 5400M (1 GB VRAM) with Optimus Technology

and pci configuration of:

-[0000:00]-+-00.0 8086:0154

+-02.0 8086:0166

+-16.0 8086:1e3a

+-19.0 8086:1502

+-1a.0 8086:1e2d

+-1b.0 8086:1e20

+-1c.0-[02]----00.0 1180:e823

+-1c.1-[03]----00.0 8086:4238

+-1c.2-[04-0b]--

+-1d.0 8086:1e26

+-1f.0 8086:1e55

+-1f.2 8086:1e03

\-1f.3 8086:1e22

Status

Thanks for your interest in Lenovo T530 port. Issues:

- EHCI output failure after sysagent

- no S3

- no MRC cache

- MRC needs watchdog

- yellow USB port isn't powered in power-off state.

(Tested on X230 *not tested* on the T530):

- RAM module combinations of 8G+8G

- USB (both 2.0 and 3.0 ports)

- Video (both internal and VGA)

- Expresscard slot (including hotplugging)

- Sound (integrated speakers, integrated mic, external headphones, external mic)

- LAN

- mini-PCIe slots (both wlan and wwan)

- Linux (through GRUB-as-payload)

- Windows (through GRUB-as-payload loading SeaBIOS image from disk; you have to use extracted VGA blob, dumped from memory isn't good enough)

- SD card slot

- Thermal management

- Fingerprint reader.

- Webcam

- Keyboard backlight

- Thinklight.

- bluetooth

- dock

- msata (fixed in commit c8f54a1109072706e2fa091dc9ab4ad3eb057b42)

Not tested:

- mini displayport (probably works)

Proprietary components status

- CPU Microcode (optional)

- VGA option rom

- MRC

- ME(Management Engine) => you do not have to touch it(just leave it where it is)

- EC(Embedded Controller) => you do not have to touch it(just leave it where it is)

GPIO layout

This information should not be considered reliable in any way, shape or form

- GPIO57 - OUT - controls..

General Purpose Events layout

- GPE? - EC SCI

- GPE? - EC SMI

Flashing

T530 has 2 flash chips of 8M and 4M. They're concatenated to one virtual flash chip of 12M which is itself subdivided in roughly in 4 parts:

- Descriptor (12K)

- ME firmware (5M-12K)

- System flash (7M)

ME firmware is not readable. Vendor firmware locks the flash and so you need to flash externally (unless until someone figures out a way around it).

Proceeds as follows:

- Turn off your laptop, remove battery and AC adapter.

- Remove the keyboard.

- Connect your external SPI flasher to the top SPI chip which is under palm resting space, on left side of the board. It's a 4M chip. IF you've chosen CBFS_SIZE 4M or smaller that's the only chip you need to reflash.

I recommend using SOIC clip. Depending on the flasher you use, you may have to use separate 3.3V source. Make sure not to feed more than 3.3V ot the chip. I used buspirate as flasher and 3.3V power lines from another computer.

- Read the flash. Twice. Compare the files to be sure. Save a copy of it on

external media.

flashrom -p <yourprogrammer> -r flash.bin flashrom -p <yourprogrammer> -r flash2.bin diff flash.bin flash2.bin

If they don't match, do not proceed. If the file is 8M, you're flashing wrong chip, connect to the right one.

- Write the flash. Since you have to write only top 4M, first split out those 4M:

dd of=top.rom bs=1M if=build/coreboot.rom skip=8

- Use flashrom to flash top.rom.

If you have trouble reading the chip successfully, the most common problems are

- insufficient power supply

- bad contacts

- too long wires

- bad pinout

The cable shipped with buspirate was too long, and needed to be trimmed.

See also In-System Programming